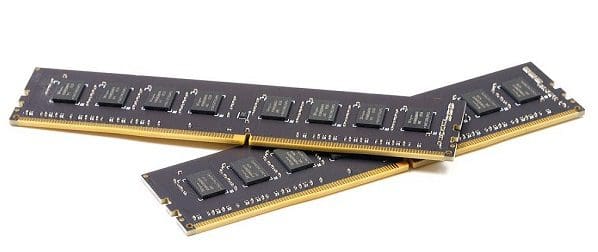

If you’re not really into computers all that much, it’s pretty reasonable for you to think that the extent of structure within RAM is the number of DIMMs plugged into the motherboard. You might know memory channels if you’re a bit more technical. You may even know about the row and column addressing system. Realistically all of that is pretty easy to grasp. Data is stored in a 2-dimensional array of rows and columns, and there can be more than one channel to access the memory.

Unfortunately, that picture isn’t correct. There are three more whole dimensions to the array. Unfortunately, the number of dimensions does make it a little hard to visualize the actual addressing configuration. The other three dimensions are, respectively: rank, chip, and bank.

Each channel can have one or more DIMMs populating it. A DIMM may have one, two, four, or eight ranks, though four and eight-rank DIMMs are essentially exclusively supported in servers. Each rank has multiple chips, each chip has numerous banks, and data in a bank can be addressed via row and column addresses.

What Is a Rank?

A rank is a grouping of DRAM chips on a DIMM all connected to the same chip select. This is critically important to understand. A chip select essentially is the rank. No matter how many physical DRAM chips are connected to the chip select, it sees them all as one and can’t control them individually. Any request from the chip select goes to all its subordinate chips. The request then contains a bank number; each chip will open that bank and, within that bank, open the row and column.

So a rank is a collection of DRAM chips on a DIMM that cannot be logically separated. The result of a read request from a rank is the concatenated result from the specified bank, row, and column on each of the chips.

Ranks can be independently queried in an overlapping fashion. However, they share the same data pins, so only one rank per channel can send or receive data at any time.

Note: Ranks can essentially operate simultaneously. While one rank opens a row, another can open another. They cannot transmit that data to the system simultaneously, though, as they’re both connected by the same channel and utilize the total bandwidth of that channel.

An Explained Example

Let’s start with a standard single-channel system. The channel is 64 bits wide. In that channel, there is one DIMM with one rank. That rank has eight chips. To saturate the 64-bit channel, each chip must provide 8 bits of data.

If the DIMM from the above example has two ranks, it may now have 16 chips. Each rank can be individually instructed independently of the other rank. However, each chip in a rank still needs to provide 8 bits of data to saturate the 64-bit data bus. Only one rank can transmit or receive data at once. Operations can be interleaved so that as soon as the first rank completes its transmission, the second rank can start its own.

What’s the Actual Difference?

Typically, in consumer hardware, a single-rank DIMM will only have DRAM chips on one side of the memory stick. Dual-rank DIMMs tend to have DRAM chips on both sides. This logic breaks down with quad- and octal-rank DIMMs. Therefore, it is helpful to remember that the number of sides of the DIMM populated with DRAM chips may not indicate the number of ranks.

It would be best if you looked at the label to identify the number of ranks on a DIMM. Typically there will be a note indicating something along the lines of 1Rx4, 1Rx8, or 2Rx8. The 1R/2R part shows the number of ranks, whereas the x4/x8 refers to the number of banks on a chip.

Tests have shown a very small performance benefit for dual-rank DIMMs over single-rank DIMMs. This is likely due to the efficiency gains thanks to the interleaving and pipelining of requests. The margin of difference, however, is generally tiny.

Conclusion

A memory rank is a chip selected on a DIMM. This chip select controls an array of DRAM chips. While the chip select can see the individual DRAM chips, it can’t address them individually. It presents them to the memory controller via the channel as a single chip, hiding the complexity. One way to think of a chip select is as a channel bifurcator, splitting the channel into as many sub-channels as DRAM chips under its control. What are your thoughts? Don’t forget to leave your comments below.